基于Quartus的數字電子鐘設計 實現計時、校時、鬧鐘、秒表及音頻功能

數字電子鐘是數字電路設計的經典應用之一,它結合了時序邏輯、組合邏輯以及用戶交互功能。本項目基于Quartus II軟件平臺,設計并實現了一個多功能數字電子鐘,具備計時、校時、鬧鐘、秒表和音頻提示功能。以下將詳細介紹電路設計思路、關鍵模塊實現方法,并提供工程文件分享。

一、系統總體設計

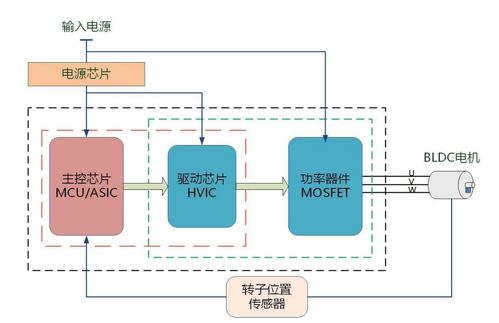

數字電子鐘系統主要由以下模塊組成:時鐘源模塊、計時模塊、校時控制模塊、鬧鐘模塊、秒表模塊和音頻輸出模塊。系統采用FPGA或CPLD作為核心控制器,通過Quartus進行邏輯設計、仿真和下載。

二、各模塊設計與實現

- 時鐘源模塊:使用晶振提供基準時鐘信號,通過分頻電路生成1Hz信號用于計時。在Quartus中,可通過計數器實現分頻,例如將50MHz時鐘分頻至1Hz。

- 計時模塊:采用BCD計數器實現時、分、秒的計數,并通過七段數碼管顯示。設計時需注意進位邏輯,例如秒計滿60向分進位,分計滿60向時進位,時計滿24歸零。

- 校時模塊:通過按鍵輸入實現時間和鬧鐘的調整。使用消抖電路處理按鍵信號,通過狀態機控制校時模式(例如按一次鍵進入小時調整,再按進入分鐘調整)。

- 鬧鐘模塊:設置鬧鐘時間并存儲,當計時時間與鬧鐘時間匹配時,觸發音頻輸出。可通過寄存器存儲鬧鐘值,并設計比較器進行時間匹配檢測。

- 秒表模塊:獨立于主計時功能,實現啟動、暫停、復位操作。使用計數器記錄秒表時間,并通過控制邏輯管理狀態切換。

- 音頻模塊:當鬧鐘觸發或秒表達到特定時間時,輸出音頻信號。可采用PWM(脈沖寬度調制)或簡單方波驅動蜂鳴器,實現不同頻率的提示音。

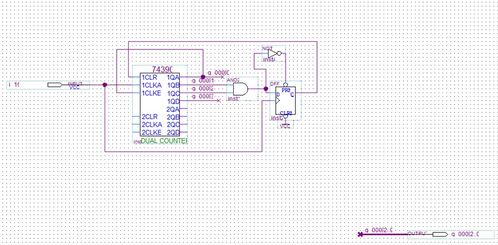

三、電路圖設計與工程文件

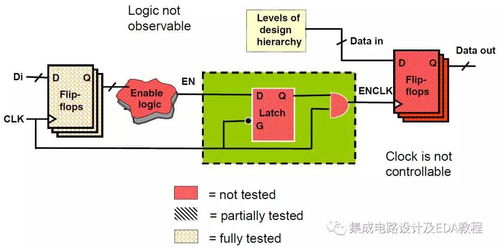

在Quartus中,設計采用原理圖輸入方式,結合VHDL或Verilog代碼實現復雜邏輯。關鍵電路包括:

- 分頻器電路:用于生成1Hz和音頻所需頻率。

- BCD計數器和顯示驅動:驅動數碼管顯示時間。

- 按鍵輸入處理電路:包括消抖和狀態控制。

- 音頻生成電路:基于計數器的方波發生器。

工程文件包括:

- 頂層原理圖文件(.bdf)

- VHDL/Verilog模塊文件(.vhd或.v)

- 引腳分配文件(.qsf)

- 仿真波形文件(.vwf)用于功能驗證

四、集成電路設計服務

對于更復雜的應用,可提供集成電路設計服務,包括:

- 定制化數字電子鐘IP核設計

- 多時鐘域管理優化

- 低功耗設計(適用于便攜設備)

- 系統集成與測試支持

五、總結

本設計通過Quartus平臺實現了功能豐富的數字電子鐘,涵蓋了從基礎計時到高級交互功能。該方案注重模塊化設計,便于擴展和修改。工程文件和電路圖可供學習和二次開發,適合數字電路實驗和嵌入式系統入門。未來可進一步添加溫度顯示、藍牙控制等功能,提升實用性。

注:工程文件及詳細電路圖可通過聯系作者獲取,確保遵循開源協議用于教育和研究目的。

如若轉載,請注明出處:http://m.021zx.cn/product/37.html

更新時間:2026-02-23 22:25:52