推挽輸出與開漏輸出 軟件開發中的硬件接口理解與應用

在嵌入式軟件開發中,深入理解硬件接口的工作模式是編寫穩定、高效代碼的基礎。推挽輸出(Push-Pull Output)和開漏輸出(Open-Drain Output)是兩種常見的數字輸出電路結構,它們在軟件配置、驅動能力和應用場景上有著顯著差異。掌握這些差異,對于軟件工程師進行外設驅動開發、通信協議實現及系統功耗優化至關重要。

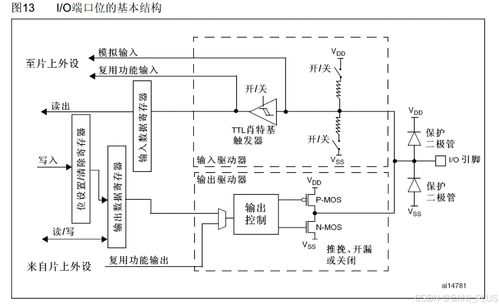

一、核心概念與硬件原理

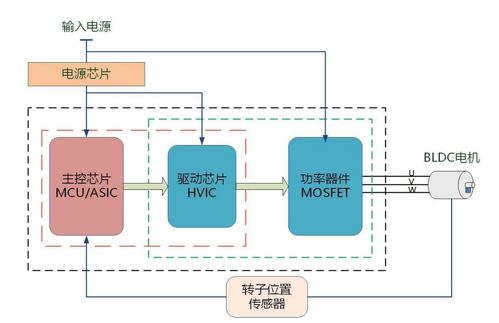

推挽輸出采用兩個晶體管(通常為MOSFET)組成推挽結構。其中一個負責將輸出拉高至電源電壓(如VCC),另一個負責將輸出拉低至地(GND)。在任意時刻,只有一個晶體管導通,使得輸出電平要么為高(邏輯1),要么為低(邏輯0),具有明確的驅動能力和低輸出阻抗。其優點在于能夠直接驅動較大電流負載(如LED、小型繼電器),且信號邊沿陡峭,適合高速數字信號傳輸。

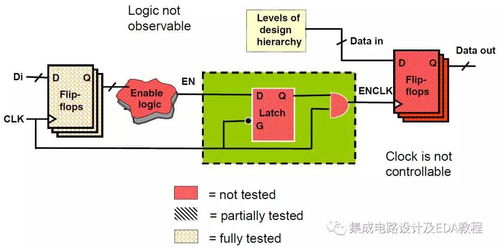

開漏輸出(在CMOS工藝中常稱為開集輸出,Open-Collector)僅使用一個下拉晶體管連接到地,而沒有內部上拉至電源。當晶體管關閉時,輸出處于高阻態(懸空);當晶體管導通時,輸出被拉低至地(邏輯0)。因此,開漏輸出本身無法主動輸出高電平,必須依賴外部上拉電阻連接到電源,才能實現完整的高低電平輸出。這種結構支持“線與”(Wired-AND)功能,即多個開漏輸出可以直接連接在一起,通過外部上拉電阻共享,任一輸出拉低則總線為低。

二、軟件開發中的配置與操作

在軟件層面,這兩種輸出模式通常通過微控制器的GPIO(通用輸入輸出)寄存器進行配置。以常見的ARM Cortex-M系列微控制器為例:

- 推挽輸出配置:在初始化階段,軟件需設置GPIO模式寄存器為輸出模式,并選擇推挽類型。例如,在STM32的HAL庫中,可通過

GPIO<em>InitStruct.Mode = GPIO</em>MODE<em>OUTPUT</em>PP進行設置。輸出電平時,直接寫入輸出數據寄存器(如HAL<em>GPIO</em>WritePin())即可控制高低電平,無需外部電路干預。

- 開漏輸出配置:配置為開漏模式(如

GPIO<em>MODE</em>OUTPUT_OD)。此時,軟件在輸出高電平時,實際上只是關閉了下拉晶體管,輸出依靠外部上拉電阻拉到高電平。因此,在驅動開漏輸出時,需要確保外部上拉電阻已正確連接,否則讀取引腳電平可能不確定。開漏輸出特別適用于雙向通信總線(如I2C),因為同一引腳可以兼作輸入和輸出,通過“線與”機制實現多主設備仲裁。

三、典型應用場景與軟件策略

- 推挽輸出的應用:

- 直接驅動負載:如控制LED亮滅、蜂鳴器發聲,軟件只需簡單寫入高低電平。

- 高速數字接口:如SPI、USART的TX引腳,要求快速電平切換,推挽輸出能提供清晰的信號邊沿。

- 電源開關控制:通過驅動MOSFET柵極,控制大功率電路通斷。

- 開漏輸出的應用:

- I2C通信協議:I2C的SDA和SCL線必須使用開漏輸出,以支持多設備共享總線。軟件在實現I2C驅動時,需注意釋放總線(輸出高電平)實則是將引腳配置為高阻,依賴上拉電阻拉高。

- 電平轉換:當不同電壓域的器件需要通信時(如3.3V MCU與5V傳感器),開漏輸出配合外部上拉至目標電壓,可以安全實現電平匹配,避免損壞低壓器件。

- 中斷共享與喚醒信號:多個開漏輸出連接至一個中斷引腳,任一設備拉低即可觸發中斷,軟件再通過輪詢識別中斷源。

四、軟件設計注意事項

- 上拉電阻配置:使用開漏輸出時,軟件工程師需與硬件工程師確認上拉電阻的值(通常1kΩ~10kΩ),電阻過大會導致上升沿緩慢,影響通信速率;過小則增加功耗。在軟件模擬時序(如I2C、One-Wire)時,需根據實際上升時間調整延時。

- 初始狀態管理:系統上電時,GPIO狀態可能不確定。軟件應在初始化階段明確設置輸出模式及初始電平,特別是開漏輸出,若意外輸出低電平可能導致總線沖突。

- 功耗優化:推挽輸出在靜態時可能產生穿透電流(如果同時導通,但現代MCU通常避免),而開漏輸出在高電平狀態依賴上拉電阻,會有持續電流消耗。在低功耗設計中,需合理選擇模式,并在空閑時將引腳切換為高阻輸入或推挽輸出固定電平。

- 故障診斷:在調試通信故障時,軟件可配合邏輯分析儀,檢查開漏總線的上升時間是否過慢(由上拉電阻和寄生電容導致),這可能需要軟件降低通信速率或調整硬件參數。

五、

推挽輸出和開漏輸出是嵌入式軟件與硬件交互的橋梁。軟件開發者不能僅停留在配置寄存器層面,而應理解其電路特性,從而做出合理的設計選擇:推挽輸出適用于需要強驅動、高速單端信號的場景;開漏輸出則為共享總線、電平轉換和雙向通信提供了靈活解決方案。在實際項目中,結合具體硬件手冊和協議要求,正確配置并優化這些接口,是提升系統可靠性、性能及能效的關鍵一步。通過軟硬協同的思維,開發者能夠更高效地解決復雜的嵌入式系統挑戰。

如若轉載,請注明出處:http://m.021zx.cn/product/49.html

更新時間:2026-02-23 20:38:37