集成電路設(shè)計與軟件開發(fā) 協(xié)同推動現(xiàn)代科技發(fā)展

集成電路設(shè)計圖片和軟件開發(fā)在現(xiàn)代電子技術(shù)領(lǐng)域中扮演著關(guān)鍵角色,它們相互促進,共同推動了智能設(shè)備、通信系統(tǒng)及工業(yè)自動化等方面的飛速進步。本文將探討集成電路設(shè)計的基本流程、軟件開發(fā)在設(shè)計中的作用,以及兩者的緊密聯(lián)系。

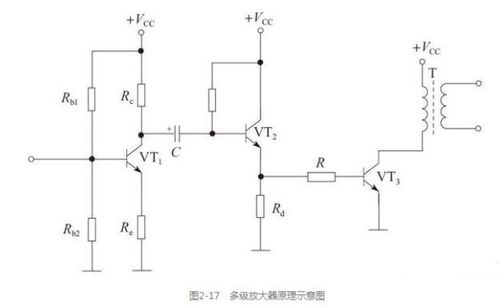

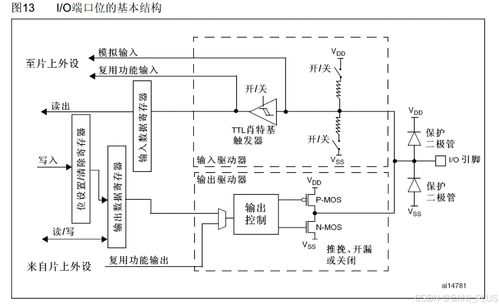

集成電路設(shè)計涉及將電子電路集成到微小的芯片上,以提高性能、降低功耗和成本。設(shè)計過程通常包括以下幾個階段:系統(tǒng)規(guī)格定義階段確定芯片的功能需求和性能指標;前端設(shè)計階段通過硬件描述語言(如Verilog或VHDL)創(chuàng)建邏輯電路模型;接著,后端設(shè)計階段進行物理布局和布線,生成集成電路設(shè)計圖片,如版圖(layout);通過仿真和測試驗證設(shè)計的正確性。這些設(shè)計圖片不僅是制造的基礎(chǔ),還為軟件開發(fā)提供了硬件接口信息。

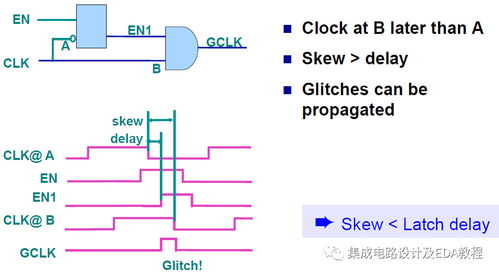

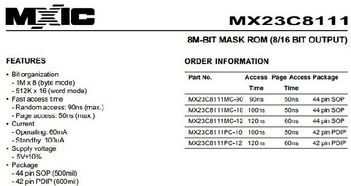

軟件開發(fā)在集成電路設(shè)計中不可或缺。一方面,設(shè)計工具如EDA(電子設(shè)計自動化)軟件(例如Cadence或Synopsys)用于建模、仿真和優(yōu)化電路設(shè)計;這些工具依賴于高效的算法和用戶界面,幫助工程師快速迭代設(shè)計。另一方面,集成電路的固件和驅(qū)動程序開發(fā)是軟件與硬件交互的橋梁,確保芯片能夠在實際應(yīng)用中正常運行。例如,在智能手機中,軟件開發(fā)人員利用集成電路設(shè)計圖片來編寫驅(qū)動程序,優(yōu)化電源管理和信號處理。

集成電路設(shè)計圖片與軟件開發(fā)的協(xié)同作用體現(xiàn)在多個層面。設(shè)計階段的仿真軟件可以模擬電路行為,及早發(fā)現(xiàn)潛在問題,減少物理原型制作的成本。隨著AI和物聯(lián)網(wǎng)的發(fā)展,軟件定義硬件(SDH)概念興起,允許通過軟件更新來調(diào)整集成電路功能,這要求設(shè)計圖片具備可編程性。在制造過程中,軟件工具用于生成掩模版圖和測試程序,確保芯片質(zhì)量。

集成電路設(shè)計圖片和軟件開發(fā)是現(xiàn)代科技創(chuàng)新的雙引擎。隨著工藝技術(shù)的進步,如7納米以下制程,設(shè)計復雜度增加,軟件工具的作用愈發(fā)重要。未來,兩者的深度融合將進一步推動邊緣計算、人工智能芯片等前沿領(lǐng)域的發(fā)展。企業(yè)應(yīng)加強跨學科合作,投資于EDA工具和軟件開發(fā),以保持競爭優(yōu)勢。通過整合設(shè)計圖片與軟件,我們可以創(chuàng)造出更智能、高效的電子系統(tǒng),惠及全球社會。

如若轉(zhuǎn)載,請注明出處:http://m.021zx.cn/product/25.html

更新時間:2026-02-23 11:56:15